ELEC373 - Digital Systems Design Assignment 3 (2023-2024)

Hello, dear friend, you can consult us at any time if you have any questions, add WeChat: daixieit

Department of Electrical Engineering and Electronics

|

ELEC373 - Digital Systems Design Assignment 3 MIPS Processor |

|

Module |

ELEC373 |

|

Coursework name |

Assignment 3 |

|

Component weight |

Assignment 3 = 20% |

|

Semester |

2 |

|

HE Level |

6 |

|

Lab location |

EEE Building PC labs 301, 304 as timetabled – Tuesday 1-4 |

|

Work |

Individually |

|

Timetabled time |

21 hours (3 hours per week – Tuesday 1pm – 4pm) |

|

Suggested private study |

10 hours including report writing |

|

How much time did it take you? |

Let us know anonymously viahttps://bit.ly/EEECARES |

|

Assessment method |

Individual, formal word-processed reports (Block diagrams and ASMs can be hand drawn and scanned into the report) |

|

Submission format |

Online via Canvas |

|

Submission deadline |

Assignment 3: Sunday week 8 of Semester 2 24th March 2024 |

|

Late submission |

Standard university penalty applies |

|

Resit opportunity |

Students failing the module and Assignment 3 will have an alternative assignment in the Summer |

|

Marking policy |

Marked and moderated independently |

|

Anonymous marking |

Yes |

|

Feedback |

Via comments on CANVAS submission on-line |

|

Learning outcomes |

LO1: Ability to design digital systems using the ASM design method LO2: Ability to implement digital systems using the Verilog Hardware Description Language LO3: Understanding the internal operation of a MIPS processor. |

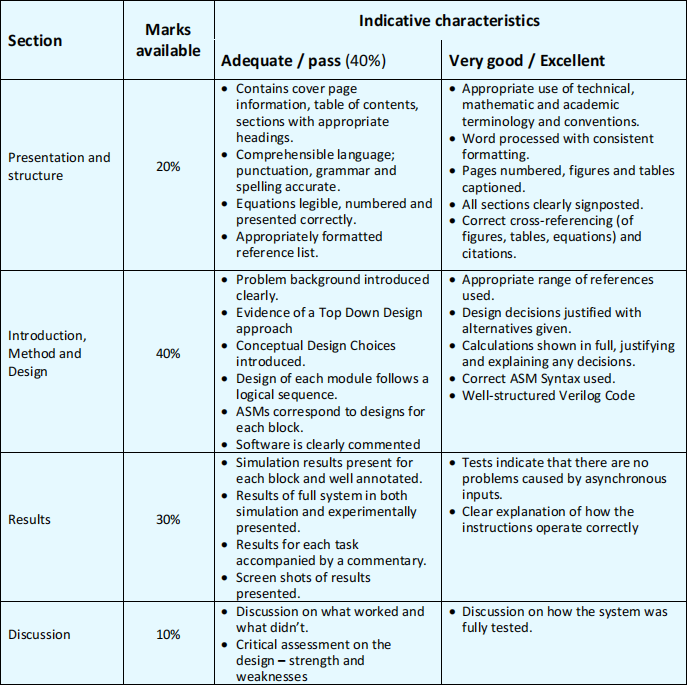

Marking Criteria

ELEC373 Verilog Assignment 3 (2023-2024)

Synthesising the MIPS Processor

Assignment Outline

Assignment 3 is split into 2 parts, Part A and Part B. The objective of Part A is to get you familiar with the synthesised MIPS single cycle processor and to write a simple programs to control the processor. Part B requires you to extend the processor so that it will implement additional instructions.

MIPS_System

The Verilog Code for the MIPS single cycle implementation are available on CANVAS. Download the ZIP file called MIPS_System and extract it into a suitable location. The synthesised MIPS processor starts executing a program from location 0x0000000. The program is loaded into the FPGA via a Memory Initialisation File, when you program the FPGA. In this design the file is called “insts_data.mif”. If you examine this file using the Quartus software you’ll find that the data it contains is:

0x3C020000, 0x24420055, 0x3C03FFFF, 0x24632008, 0xAC620000, 0x08000005

If you disassemble this you’ll find that the first instruction corresponds to: lui $2, 0x0000

Using the MIPS Instruction Coding available from CANVAS, disassemble the other instructions to understand what the program does.

Memory Map

If you study the “Addr_Decoder.v” file you’ll find that the GPIO (General Purpose Input/Output) module is mapped from location 0xFFFF_2000. If you examine the “GPIO.v” file you’ll find the individual locations for the LEDs and switches on the DE2 board.

Program Execution

Compile and download the design, you should see that it switches on some of the red LEDs.

SignalTap Logic Analyser

You should configure the SignalTap logic analyser so that you can see the appropriate signals changing in the synthesised MIPS core when the MIPS CPU is running.

Assignment 3 Part A - 40%

1. Modify the MIPS assembly language program so that the program displays the lowest 8 digits of your ID on the DE2 board 7 segment display.

2. Show that your program functions correctly by taking a screen shot(s) of the SignalTap Logic analyser showing your program executing your modified programme. Make sure that the

instruction and programme counter can be read.

3. In your report you should include your assembly language code and a screen dump of the

SignalTap Logic analyser. Also include a photograph of the 7 segment displays showing your ID.

Assembling

You may find that hand-assembly is quite error prone and laborious. On CANVAS you’ll find a

MIPS assembler (MARS 4.1) written in JAVA that will help you assemble your code. To get this to assemble code starting at location 0x0000000, select “Settings->Memory Configuration->Compact, Text at Address 0” that will ensure that any jumps have the correct memory location encoded.

Assignment 3 Part B - 60%

The MIPS design presented in MIPS_System only implements a limited number of the MIPS instructions. For the R-Type instructions ADD, ADDU, SUB, SUBU, AND, OR and SLT are implemented. Your task is to modify the MIPS design so that it implements the additional instructions shown in Table 1 whilst still ensuring the existing instructions work correctly. Once you have modified your design you need to write programs to demonstrate that your hardware correctly implements the instructions. Your results should include print outs of the SignalTap logic analyser showing your program operating. Annotate the print out to explain what is happening. You should submit an electronic copy of your design and assembly language programs onto CANVAS. Your written report should explain what modifications you have made to the Verilog code and include the Verilog code you have developed. There is no need to include the Verilog code for the modules you haven’t modified. You should also include ASM/ASMD charts for your modified code. For your report on instruction 3 you should include a block diagram showing the extra data pathways you have added.

2024-03-18

Synthesising the MIPS Processor